Building an ML Accelerator from Scratch on an FPGA

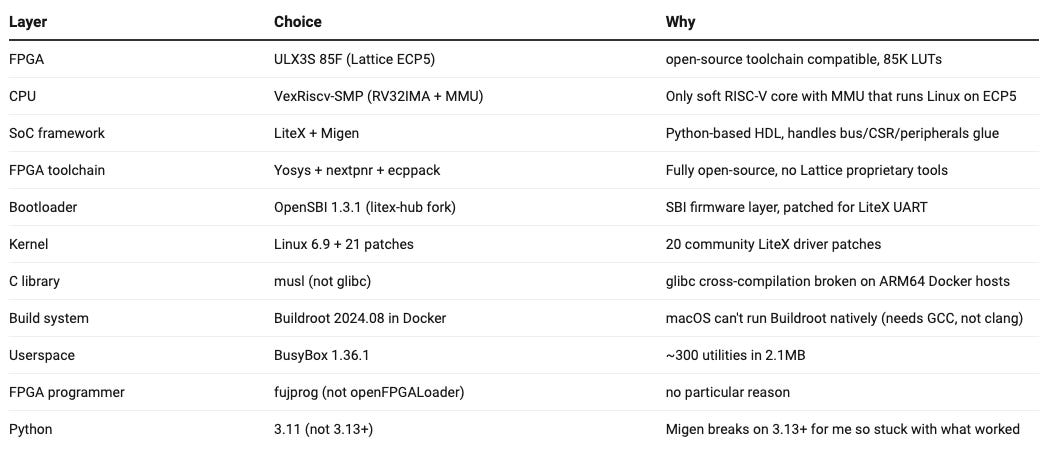

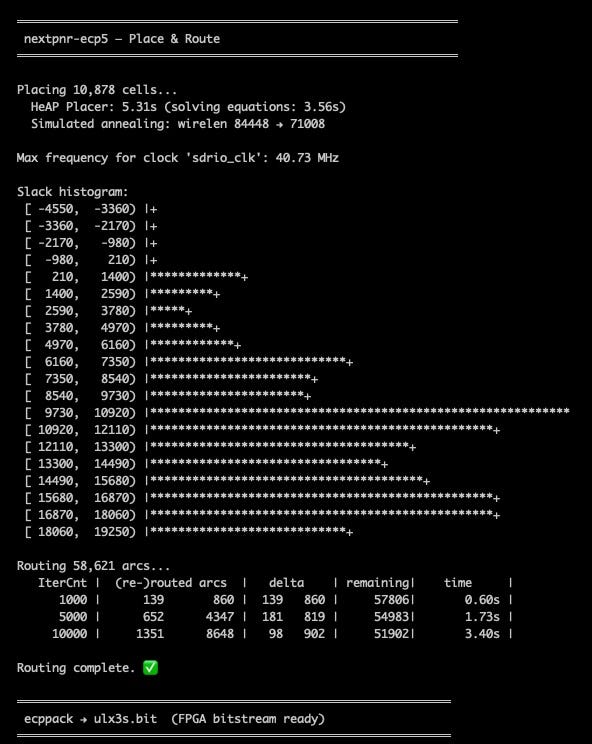

I’m designing a hardware ML accelerator for a RISC-V FPGA SoC, targeting the ULX3S board (Lattice ECP5). The SoC already boots Linux 6.9 and does matrix multiplication in combinatorial logic at zero-cycle latency.

Next milestone is full neural network inference.

I’ll be documenting the build process here as it progresses, the architecture decisions, the tradeoffs, the things that break.

If you’re interested in edge ML, FPGA development, or just like watching someone build a thing from the ground up, stick around.